The PCI Special Interest Group (PCI-SIG) recently released a new revision or draft, if you will, of the PCIe 7.0 specifications. As per the group’s member who are scouring through every detail, there is positive news that the interface specification is progressing as planned, as there have been minimal changes since the last draft.

“As we enter 2025, I am pleased to announce PCIe 7.0 specification, version 0.7 is now available for member review. This specification version incorporates all the feedback we received from members on version 0.5 released in April 2024 and brings us one step closer to the full release of the PCIe 7.0 specification, targeted for 2025.”

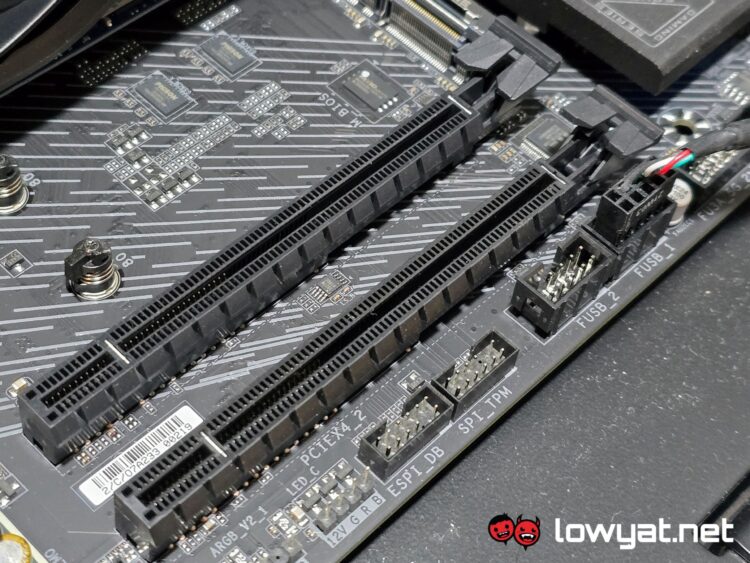

The PCIe 7.0 interface aims to double the bandwidth of PCIe 6.0, from 64GT/s to a whopping 128GT/s of raw bit rate, and up to 512GB/s bi-directionally via the x16 configuration. To put that into another comparison point, the interface aims to deliver 16GB/s per lane, versus the 4GB/s per lane that the current PCIe 5.0 does.

As to why we’re talking about PCIe 7.0 when PCIe 6.0 isn’t even widely available to the masses, two words: forward thinking. That, and the fact that the future interface is being designed primarily for use in datacentres and AI applications. As machine learning workloads become increasingly heavy and more demanding, so too does the need for speed and high-capacity data pipelines, as well as the need to eliminate bottlenecks between components.

Follow us on Instagram, Facebook, Twitter or Telegram for more updates and breaking news.