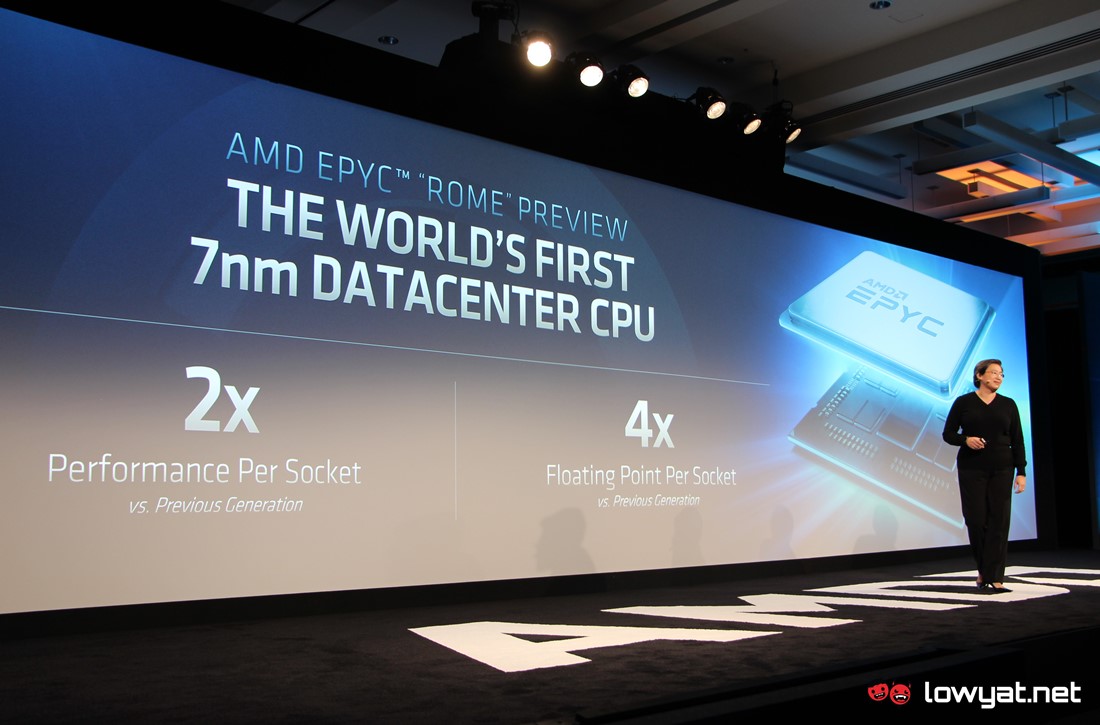

During its Next Horizon event, AMD has also taken the opportunity to release initial information regarding its upcoming datacenter-centric Epyc processors codenamed “Rome”. They will not only be the first Zen 2-based product, but they are being built using an all-new design implementation.

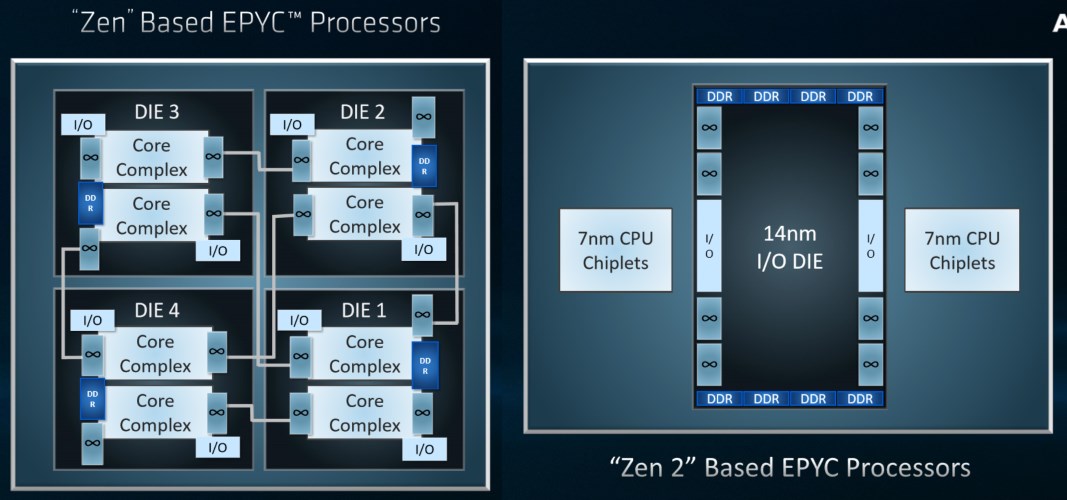

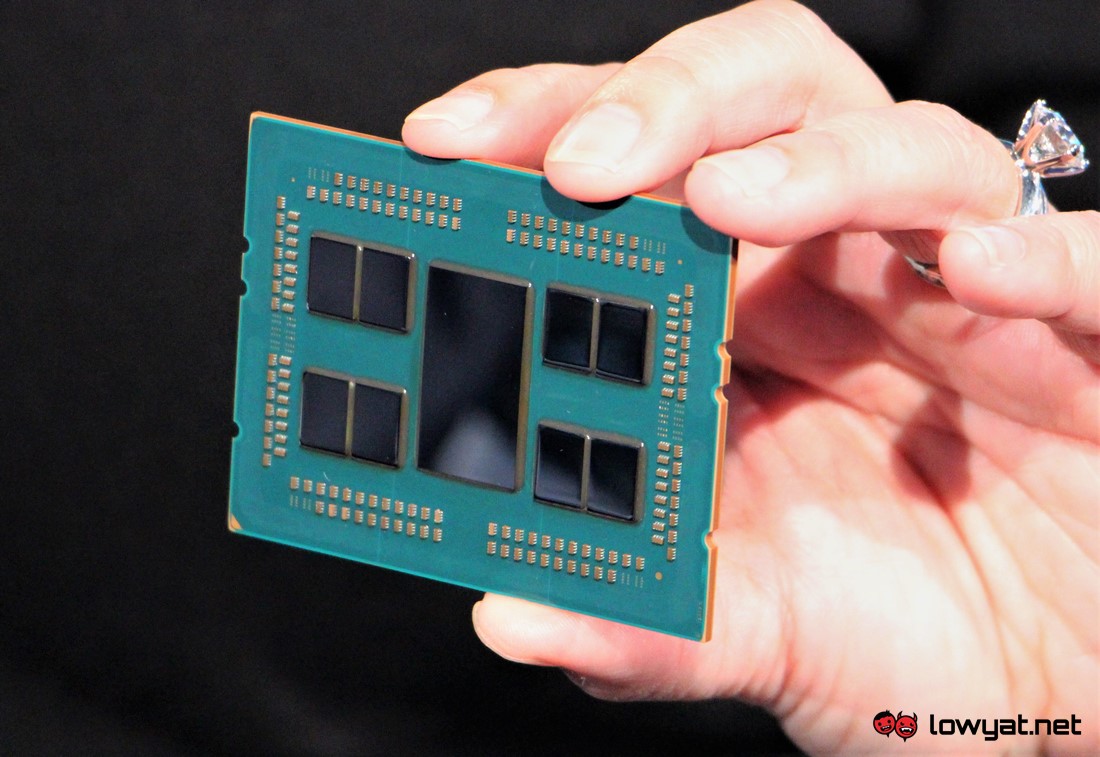

Specifically, the new Epyc Rome processors will feature a combination of 7nm Zen 2 CPU chips alongside another 14nm die that controls the input and output elements of the processor. The CPU chips which are called chiplets by AMD are connected to the I/O die through an “enhanced version” of the company’s Infinity Fabric interconnect link.

As a comparison, the I/O portions such as the memory, PCIe, USB, and SATA support for the existing Epyc 7000 series processors are contained within their CPU modules itself. These modules communicate to each other via the first generation Infinity Fabric.

According to AMD, the dedicated I/O die offers improved latency and power consumption for the new Epyc Rome processors. Together with higher instructions-per-clock, they will be made available with up to 64 Zen 2 CPU cores which are twice the amount of maximum CPU cores that are being offered by the current generation of Epyc processors.

Epyc Rome processors are also able to support PCIe 4.0 standard which should be able to help improve the performance of accelerators such as the newly announced AMD Radeon Instinct MI60 which supports the same standard. They will also continue to be compatible with the SP3 CPU socket that is being used by the current Epyc lineup.

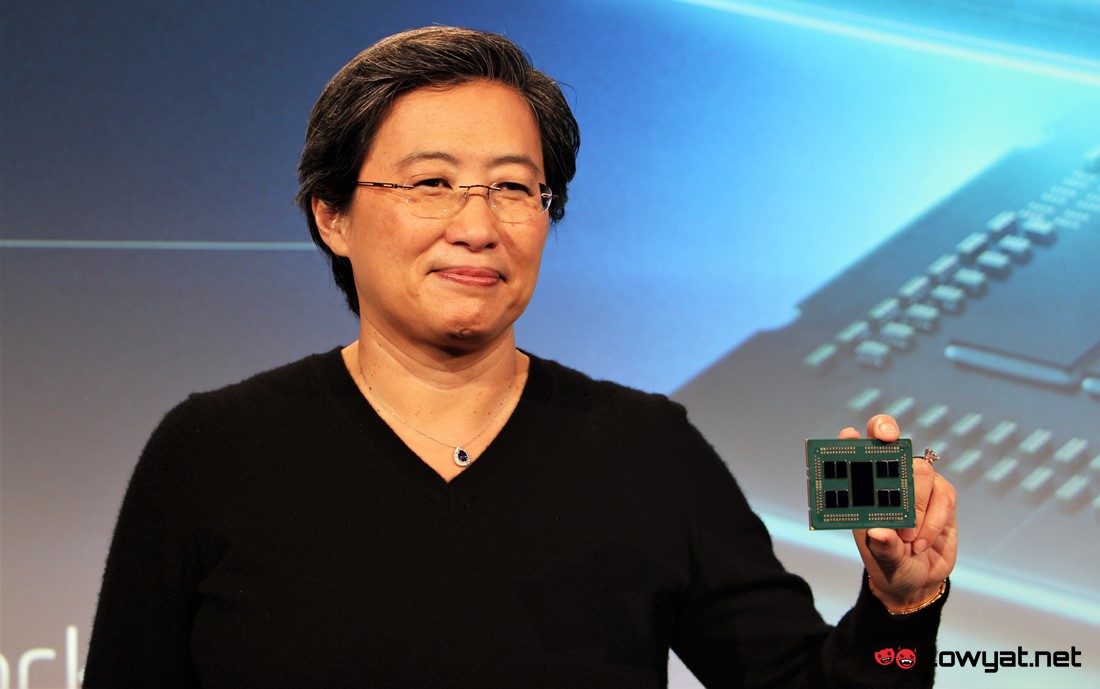

In terms of overall improvements, AMD has stated that Epyc Rome processors will be able to deliver up to 2x performance and 4x floating point per socket than the existing lineup of Epyc processors. However, the company didn’t provide any specifications of these processors during the event which we will likely hear more about them as we get closer to their release next year.

Follow us on Instagram, Facebook, Twitter or Telegram for more updates and breaking news.